1. Jurnal

[Kembali]

- Panel DL 2203D

- Panel DL 2203C

- Panel DL 2203S

4. Jumper

3. Rangkaian Simulasi

[Kembali] Pada rangkaian percobaan di atas terdapat 2 jenis flip flop yaitu D flip-flop (kiri), dan J-K flip-flop(kanan). Masing masing jenis flip flop tersebut memiliki kondisi tersendiri.

Untuk D flip flop :

Input pin S terhubung ke B1, input pin R terhubung ke B0, input pin D terhubung ke B5 dan Clock terhubung ke B6. output Q dan Q' terhubung LED (pada percobaan de lorenzo) atau logicprobe (pada percobaan proteus).

Mula-mula tinjau bagian R-S terlebih dahulu, apabila salah satu atau keduanya aktif, maka output tidak akan terpengaruh oleh input D. Saat R-S tidak aktif barulah input D ada pengaruh terhadap output. Output yang dihasilkan oleh input D dapat dilihat pada tabel kebenaran di bawah. Clock pada rangkaian percobaan di atas bersifat active low.

Untuk J-K flip-flop :

Input pin S terhubung ke B1, input pin R terhubung ke B0, input pin J terhubung ke B2, CLK terhubung ke B 3, input pin K terhubung ke B4. output Q dan Q' terhubung LED

Mula-mula tinjau bagian R-S terlebih dahulu, apabila salah satu atau keduanya aktif, maka output tidak akan terpengaruh oleh input J-K. Saat R-S tidak aktif barulah input J-K ada pengaruh terhadap output. Output yang dihasilkan oleh input J-K dapat dilihat pada tabel kebenaran di bawah. Clock pada rangkaian percobaan di atas bersifat active low, artinya, output akan dihasilkan ketika perpindahan nilai clock dari 1 ke 0.

5. Video Rangkaian

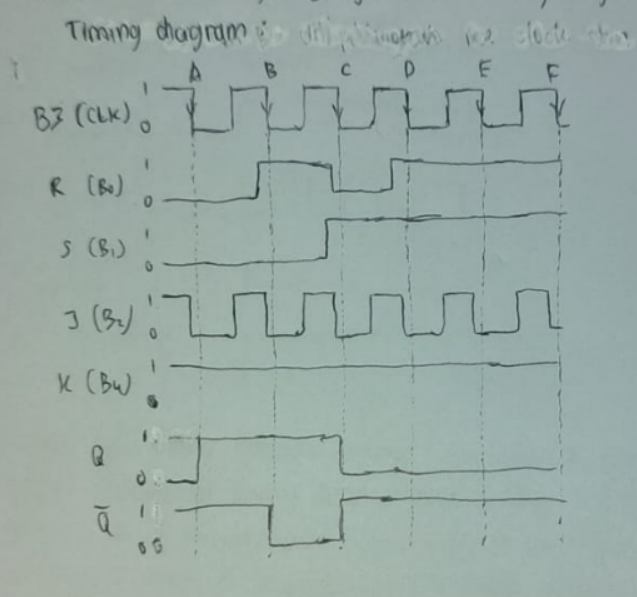

[Kembali]1. Analisa apa yang terjadi saat input B3 dan B2 dihubungkan ke clock dan k berlogika 1, gambarkan timing diagramnya !

Dapat dilihat pada diagram di atas, dari titik A sampai D, saat berada di titi ktersebut, R atau S sedang aktif, maka J dan K tidak akan mempengaruhi outout yang akan muncul, karena input J dan K akan berpengaruh saat R S tidak aktif. Kondisi yang akan dianalisa yaitu saat R dan S tidak aktif atau berlogika 1. Pada timing diagram yaitu saat titik D sampai titik F. Input R dan S tidak aktif, barulah input J dan K akan berubah ubah nilainya setiap waktu tertentu, sedangkan untuk K selalu 1. Pada tabek kebenaran saat J = 0 dan K=1, maka Q = 0, Q' = 1, Kemudian saat J = 1 dan K = 1, maka output akan berlawanan dari output sebelumnya. Pada kondisi sekarang, output akan selalu Q = 0, Q'=1, karena clock sedang fall time dan clock tersebut active low, dan juga nilai input berada J = 0 K=1. Output tidak akan pernah berlawanan dari output sebelumnya, karena saat J = 1 dan K = 1, clocknya rise time.

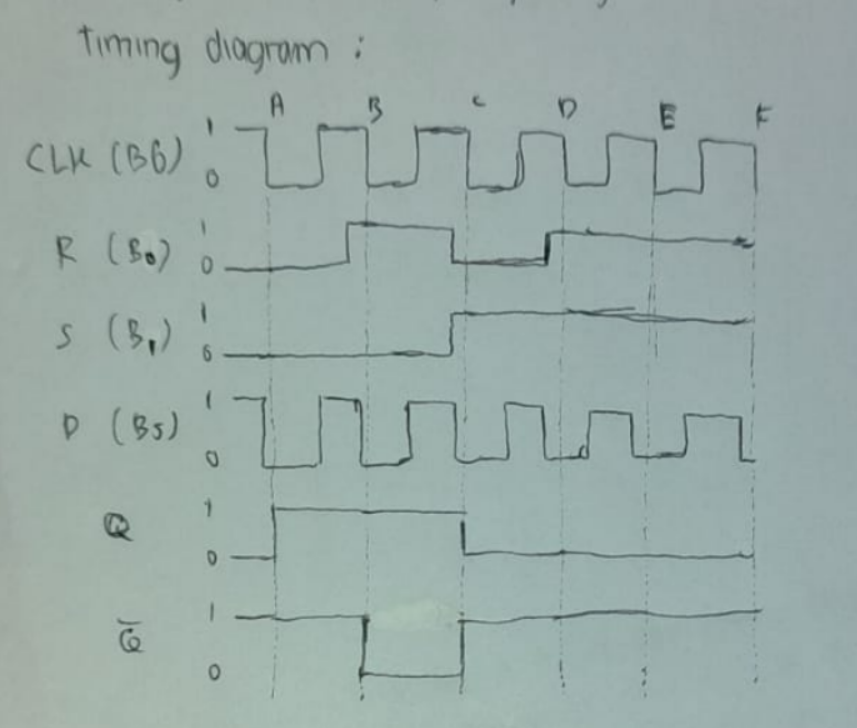

2. Analisa apa yang terjadi saat input B5 dan B6 dihubungkan ke clock, gambarkan timing diagramnya!

Dapat dilihat pada timing diagram di atas, dari titik A sampai D, kondisi tersebut merupakan kondisi dimana input R atau S aktif, maka input D tidak akan mempengaruhi output yang akan muncul. Kemudian saat titik D sampai F, barulah input D akan mempengaruhi output, karena input R dan S sudah tidak aktif saat berlogika 1. Input D merupakan input clock, yang dimana nilai D akan berubah-ubah setiap beberapa waktu tertentu. Pada tabel kebenaran, nilai D = 0, maka output Q = 0 dan Q' = 1, kemudian saat nilai D = 1, maka output Q = 1 dan Q' = 0. Pada kondisi sekarang, output akan selalu bernilai Q = 0 dan Q' = 1, karena saat nilai D = 0, clock selalu berada di fall time, clock tersebut active low, sehingga akan menghasilkan output Q = 0 dan Q' = 1. Alasan tidak terjadi output Q = 1, Q' = 0, karena saat D = 1, clock selalu berada di rise time, sehingga output Q = 1, Q' = 0 tidak bisa terjadi.

Tidak ada komentar:

Posting Komentar