2. Alat dan Bahan

[Kembali]

2.1 Alat

a.. Jumper

Gambar 1. Jumper

b.Panel DL 2203D

c.Panel DL 2203C

d.Panel DL 2203S

Gambar 2. Modul De Lorenzo

2.2 Bahan (proteus)

a. IC 74LS112 (JK filp flop)

Gambar 3. IC 74LS112

b. Power DC

Gambar 6. Rangkaian 3a sebelum dijalankan

Gambar 7. Rangkaian 3a saat dijalankan

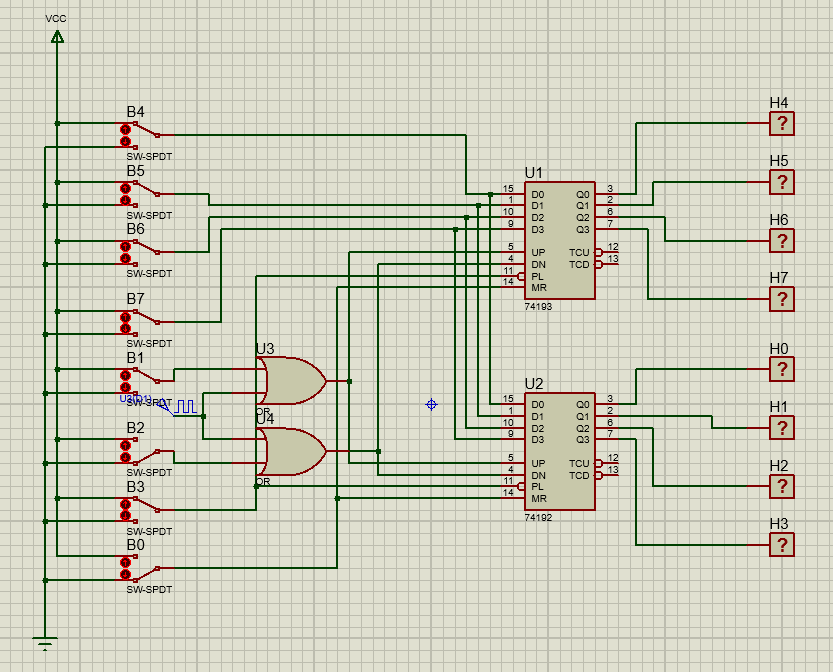

Gambar 8. Rangkaian 3b sebelum dijalankan

Gambar 9. Rangkaian 3b saat dijalankan

4. Prinsip Kerja Rangkaian [Kembali]

Rangkaian diatas merupakan rangkaian Counter synchronous, yang mana input flip flop selanjutnya berasal dari output flip flop sebelumnya. Pada rangkaian tersebut terdapat 8 saklar yang masing masing saklar tersebut terhubung ke 2 IC berbeda yaitu IC 74193 dan 74192. IC 74193 merupakan decoder bilangan hexadecimal, sedangkan IC 74192 merupakan decoder bilangan decimal. Output pada masing masing IC tersebut dihubungkan ke logicprobe. Terdapat pin UP yang berfungsi untuk menghitung bilangan dari yang minimum ke maksimum, sedangkan pin DN (Down) untuk menghitung bilangan dari yang maksimum ke minimum. PL (PLoad) untuk mempertahankan output bilangan tertinggi, PL active low, MR(Master Reset) berguna untuk mereset bilangan output ke 0.

Saat PL aktif (logika 0, karena active low) output yang dihasilkan akan sama dengan input yang diberikan ke D0,D1,D2,D3. Selain itu, saat PL aktif maka input UP dan DN tidak akan berpengaruh kepada output PL. Jadi, apabila ingin menggunakan rangkaian tersebut untuk menjadi sebagai penghitung, maka hal yang dialkukan yaitu dengan menonaktifkan PL dan MR.

Saat input DN aktif, kemudian input UP diubah ubah nilainya, maka akan terjadi perubahan nilai pada output decoder tersebut. Perubahan terjadi saat input UP dari logika 0 ke logika 1.Hal yang akan terjadi adalah decoder tersebut akan melakukan counter up, yaitu mengubah nilai dari nilai terendah ke nilai tertinggi yang dapat dicapai.

Saat input UP aktif, kemudian input DN diubah ubah nilainya, maka akan terjadi perubahan nilai pada output decoder tersebut. Perubahan terjadi saat input DN dari logika 0 ke logika 1.Hal yang akan terjadi adalah decoder tersebut akan melakukan counter down, yaitu mengubah nilai dari nilai tertinggi yang dapat dicapai ke nilai terendah.

Perbedaan pada percobaan 3a dan 3b yaitu pada rangkaian 3a count dilakukan secara manual dengan mengubah ubah logika saklar, sedankan pada percobaan 3b count dilakukan secara otomatis dengan menggunakan sinyal clock yang di OR kan dengan masing masing saklar B1 dan B2.

1. Mengapa saat PL aktif tidak count secara otomatis?

Karena saat PL aktif, IC akan berada dalam keadaan parallel load, yaitu output yang dihasilkan Q0, Q1, Q2, dan Q3 tergantung dari nilai logika pada input D0, D1, D2, dan D3, sehingga counting tidak dapat dilakukan. PL diibaratkan sebagai inputan S pada R S flip flop, maka pada saat S aktif maka Q akan bernilai 1, sehingga output akan tetap 1, tidak bisa berubah.

2. Mengapa pada saat PL mati input B1-B4 menjadi don't care?

Jika dilihat pada rangkaian dalam IC tersebut. B1, B2, B3, dan B4 terhubung dengan PL, kemudian diberi gerbang NAND seperti pada gambar dibawah ini :

Saat PL mati, maka gerbang logika NAND akan menghasilkan output 1, jadi apapun inputan dari B1, B2, B3, dan B4, tetap saja gerbang NAND akan berlogika 1, kemudian output dari NAND tersebut dihubungkan ke input S pada flip-flop, karena output NAND selalu 1, maka input S tidak aktif karena S active low, karena S tidak aktif maka Q akan selalu 0.

7. Link Download [Kembali]

- Download Rangkaian Simulasi 3a Klik Disini

- Download Rangkaian Simulasi 3b Klik Disini

- Download video simulasi Klik Disini

- Download HTML Klik Disini

- Download datasheet 74192 Klik Disini

- Download datasheet 74193 Klik Disini

- Download datasheet OR Klik Disini

- Download datasheet switch Klik Disini

- Download datasheet logicprobe Klik Disini

Tidak ada komentar:

Posting Komentar